## ЛАБОРАТОРНАЯ РАБОТА №3

# АМПЛИТУДНЫЙ ДИСКРИМИНАТОР И ФОРМИРОВАТЕЛЬ НА ЛОГИЧЕСКИХ ЭЛЕМЕНТАХ

**С.И. СВЕРТИЛОВ**

### 1. ВВЕДЕНИЕ

Как известно, непосредственно с детекторов ядерных излучений информация поступает в аналоговой форме. Для того, чтобы преобразовывать аналоговые сигналы в цифровой код используются специальные устройства, называемые *дискриминаторами* импульсов. Главной характеристикой таких устройств является величина порогового напряжения  $U_p$ . Если амплитуда сигнала на входе дискриминатора  $U$  меньше порогового напряжения:  $U < U_p$ , то на выходе сигнал не появляется (состояние «0»), если же  $U > U_p$ , то дискриминатор на какой-то интервал времени переходит в другое (квазистойчивое) состояние («1») и на его выходе появляется сигнал стандартной амплитуды. Значения напряжения, соответствующие уровням «0» и «1», задаются состояниями отсечки и насыщения транзисторов в выходных каскадах дискриминатора. Эти уровни размыты в некоторых пределах, но не перекрываются. В некоторых типах дискриминаторов сигнал на выходе не формируется, а зависит от входного сигнала, в простейших схемах при превышении входным сигналом порогового уровня на выходе появляется сигнал, повторяющий входной. В более сложных устройствах сигнал на выходе дискриминатора формируется, то есть получается сигнал стандартной формы (как правило, прямоугольный импульс), а в некоторых случаях – и стандартной длительности.

Дискриминаторы обычно подразделяют на дискриминаторы импульсов напряжения и дискриминаторы импульсов тока. Первые обычно подключают к выходам линейных усилителей напряжения, а вторые могут использоваться при работе с устройствами, которые могут быть представлены, как генераторы тока, например, подключаться непосредственно к выходу фотоэлектронного умножителя сцинтилляционного или черенковского детектора. Данная лабораторная работа посвящена изучению, в основном дискриминаторов импульсов напряжения.

Дискриминатор считается *идеальным*, если при поступлении на его вход сигнала с амплитудой, превышающей пороговое

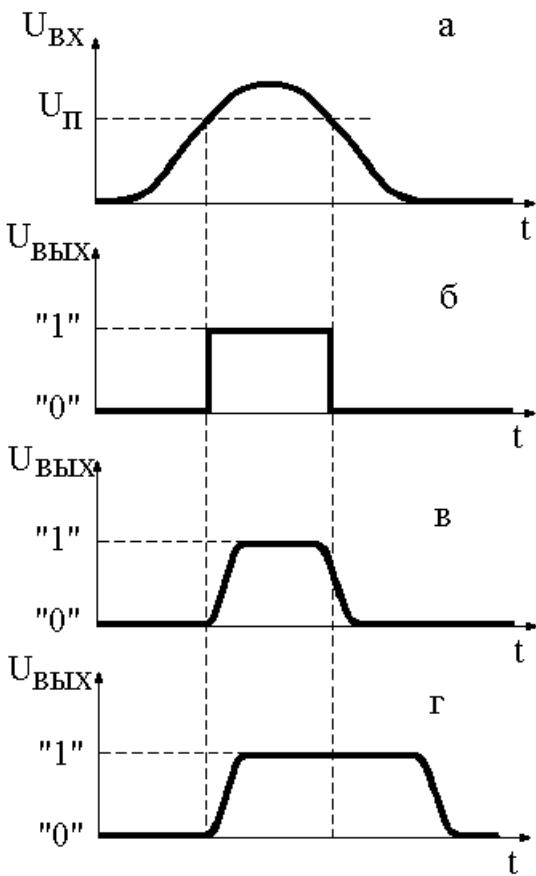

Рис. 1. Временные диаграммы идеального и реального дискриминаторов

ной времени – рис. 1г).

Все типы дискриминаторов принято подразделять на *пассивные* и *активные*. Причем активные дискриминаторы в свою очередь подразделяются на устройства, не имеющие собственную постоянную времени (*триггеры Шмитта*) и, так называемые, *формирователи*, характеризующиеся собственной постоянной времени, которой определяется длительность сформированного выходного сигнала.

Различают следующие временные характеристики дискриминатора:

- запаздывание момента его срабатывания относительно момента перехода входного напряжения через пороговый уровень;

- длительность импульсов (для формирователей);

- время нечувствительности к внешним сигналам после окончания процесса формирования импульса (мертвое время).

значение, на выходе появляется импульс с бесконечно крутым фронтом и срезом, который отличен от нуля строго в том интервале времени, когда напряжение входного сигнала превышает пороговый уровень (см. рис. 1а, 1б). В реальных дискриминаторах длительности фронта и среза выходного сигнала не равны нулю, а его продолжительность может либо равняться интервалу времени, когда амплитуда входного сигнала превышает  $U_{\text{пор}}$  (в схемах, не обладающих собственной постоянной времени – рис. 1в), либо равняться фиксированному значению (в схемах, характеризуемых собственной постоянной

В пассивном дискриминаторе все связи между транзисторами можно сделать гальваническим, поэтому на его выходе формируется импульс, длительность которого весьма незначительно может превышать интервал времени, в течение которого напряжение входного сигнала превышает пороговый уровень. Это превышение, как правило, возникает вследствие инерционности транзисторов при их выходе из насыщения. В пассивных дискриминаторах нет мертвого времени, поэтому длительность сигналов на выходе пассивного дискриминатора практически определяется длительностью входных сигналов на уровне порога (с учетом его «размытия»).

Однако у активных дискриминаторов вследствие конечного наклона их амплитудных характеристик стабильность и определенность порогов значительно меньше, чем у активных дискриминаторов. Поэтому активные дискриминаторы обеспечивают большую точность счета импульсов с амплитудой, превышающей заданный порог. В тех же случаях, когда не требуется высокой точности счета, могут использоваться и пассивные дискриминаторы, которые проще конструктивно и обладают большим быстродействием по сравнению с активными дискриминаторами.

## 2. ХАРАКТЕРИСТИКИ РАЗЛИЧНЫХ ТИПОВ ДИСКРИМИНАТОРОВ

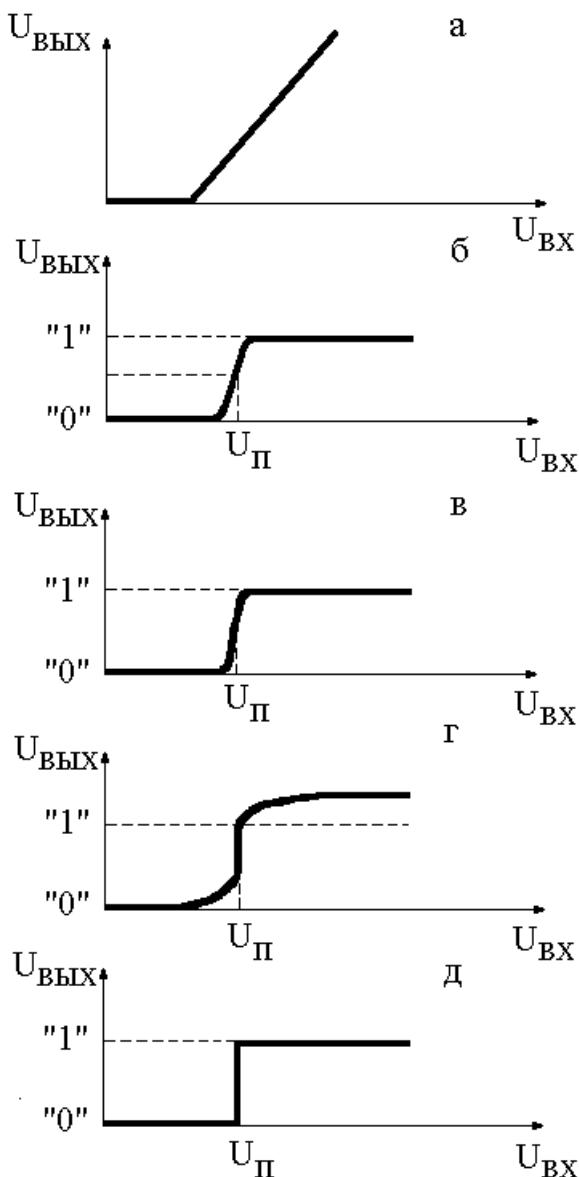

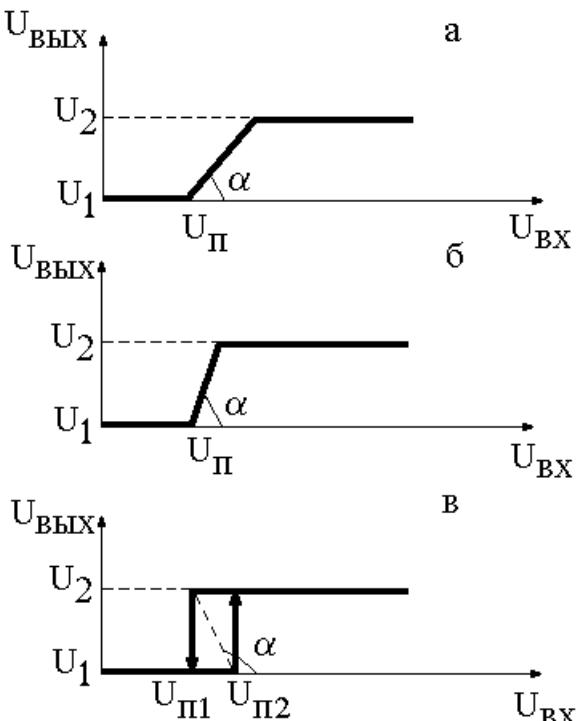

Для пассивных дискриминаторов зависимость амплитуды выходного сигнала  $U_{\text{вых}}$  от амплитуды входного сигнала  $U_{\text{вх}}$  – так называемая, амплитудная характеристика  $U_{\text{вых}}(U_{\text{вх}})$  содержит участок, для которого

$$0 < \frac{\partial U_{\text{вых}}}{\partial U_{\text{вх}}} < \infty,$$

то есть имеет вид, как на рис. 2а – 2в. Амплитудная характеристика активных дискриминаторов содержит «вертикальный» участок, для которого

$$\frac{\partial U_{\text{вых}}}{\partial U_{\text{вх}}} \rightarrow \infty,$$

то есть имеет вид, как на рис. 2г (на рис. 2д представлена амплитудная характеристика идеального дискриминатора).

Вертикальный участок на амплитудной характеристике активного дискриминатора соответствует развитию регенеративного (лавинного) процесса. В пассивном дискриминаторе лавинный

Рис. 2. Амплитудные характеристики пассивных и активных дискриминаторов

процесс не возникает, и его амплитудная характеристика имеет всегда конечный, хотя может быть и довольно крутой, наклон. Это означает, что для пассивного дискриминатора всегда есть такой диапазон амплитуд, для которого амплитуды выходных импульсов будут определяться амплитудами входных сигналов, в то время как для активных дискриминаторов при превышении входным сигналом порогового значения сразу будет вырабатываться импульс, амплитуда которого определяется самим дискриминатором и не зависит от амплитуды входного сигнала. Чем больше крутизна амплитудной характеристики, тем меньше «размытие» порогового напряжения и дискриминатор ближе к идеальному.

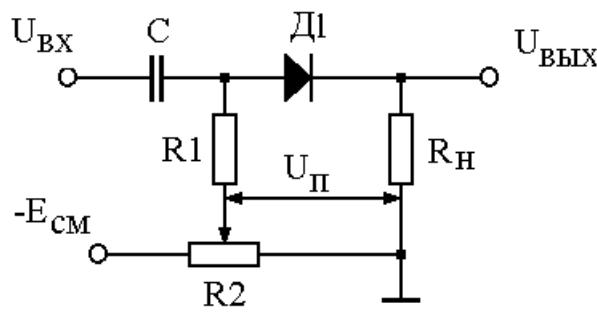

Простейшим пассив-

ным дискриминатором является дискриминатор на диоде, схема которого приведена на рис. 3. Работа диодного дискриминатора основана на резком изломе его вольт-амперной характеристики. Диод может пропускать только такие импульсы, амплитуда которых превышает напряжение запирания диода  $U_p$ , соответствующее точке излома вольт-амперной характеристики. Подобные устройства называют иногда ограничителями. Однако амплитудная характеристика подобного дискриминатора обычно имеет малую крутизну, вследствие чего не имеет резкого излома при достижении порогового напряжения (пороговая область охватывает несколько десятых вольта), а также не ограничена сверху (см. рис. 2а). Поэтому

такой дискриминатор осуществляет, по сути, только сортировку сигналов по амплитуде относительно величины  $U_{\text{п}}$ . Порог дискриминации устанавливают с помощью смещающего напряжения, которое обычно подают через резистивный делитель напряжения ( $R_1, R_2$ , см. рис. 3).

Чтобы получить пороговое устройство с выходными сигналами, стандартизованными по амплитуде, необходимо подключить диод к усилителю. Амплитудная характеристика дискриминатора на диоде с усилителем приведена на рис. 2б. Из

Рис. 3. Дискриминатор на диоде

рисунка видно, что крутизна характеристики резко увеличивается и появляется плато, обусловленное насыщением транзисторов при больших амплитудах входных импульсов. В принципе в качестве пассивного дискриминатора может использоваться любой усилитель с резко нелинейной

амплитудной характеристикой, то есть с большим коэффициентом усиления. Чем больше коэффициент усиления, тем больше крутизна амплитудной характеристики такого дискриминатора. Если коэффициент усиления настолько велик, что транзисторы усилителя входят в режим насыщения даже при очень небольших входных сигналах, наклон нелинейной части амплитудной характеристики будет близок к  $90^\circ$  (см. рис. 2в). В этом случае «размытие» порогового напряжения невелико и амплитудная характеристика близка к идеальной.

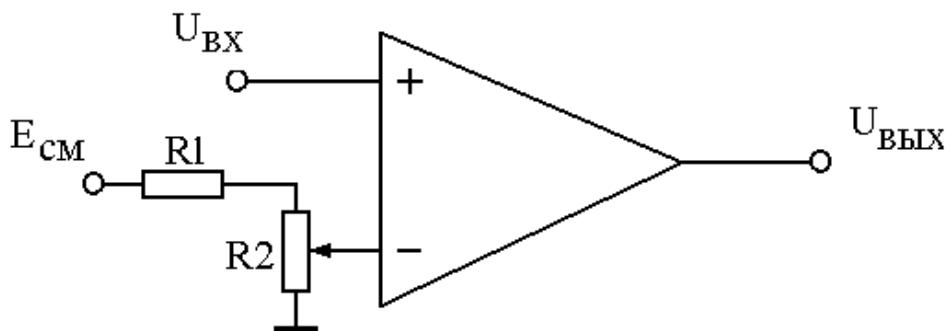

Дискриминаторы с подобной амплитудной характеристикой могут быть выполнены на основе, так называемых, *компараторов* – устройств, которые осуществляют сравнение исследуемого входного сигнала с опорным напряжением  $U_{\text{оп}}$ . Они выдают напряжение, соответствующее уровням «0» или «1» в зависимости от того, меньше или больше  $U_{\text{оп}}$  исследуемое напряжение. Компараторы, как правило, выполняют на базе операционных усилителей с очень большим коэффициентом усиления (вплоть до  $10^4$ ) в очень узком диапазоне (10-100 мкВ) разности сигналов, подаваемых на прямой и инвертирующий входы. Если разность сигналов превышает этот диапазон, компаратор находится в режиме ограничения в состоянии с уровнем напряжения на выходе, соответствующем «0» или «1» в зависимости от знака разности потенциала на входе компаратора. В

случае использования дифференциальных усилителей входное и опорное напряжение подаются на разные входы дифференциального каскада (см. рис. 4). Пороговый уровень напряжения в случае схемы, изображенной на рис. 4, устанавливают путем подбора фиксированного напряжения на одном из входов операционного усилителя. Тогда, при превышении сигнала на втором входе порогового уровня хотя бы на малую величину (несколько сот микровольт) компаратор вырабатывает на своем выходе стандартный по амплитуде сигнал, длительность которого равна времени, в течение которого на его втором входе присутствует сигнал, превышающий пороговый уровень. Лучшие характеристики дискриминирующих устройств на компараторах могут быть получены при использовании внешней резистивной (гальванической) или емкостной положительной обратной связи, реализующей активные дискриминаторы типа триггеров Шмитта и формирователей (одновибраторов).

Рис. 4. Компаратор.

Активным дискриминатором является любой усилитель с положительной обратной связью. Коэффициент усиления такого усилителя может быть представлен в виде:

$$K \approx \frac{K_0}{1 - BK_0},$$

где  $K_0$  – коэффициент усиления без обратной связи,  $B$  – коэффициент обратной связи.

На рис. 5 приведены амплитудные характеристики усилителя с положительной обратной связью для разных значений  $BK_0$ . Амплитудная характеристика для случая  $BK_0 = 0$  изображена на рис. 5а. Наклон этой характеристики характеризуется углом  $\alpha$ , для которого  $\operatorname{tg}\alpha = K_0$ . Минимальное ( $U_1$ ) и максимальное ( $U_2$ ) значения выходного напряжения соответствуют запиранию и насыщению транзисторов усилителя. Эти значения определяются внутренним

устройством усилителя и не зависят от глубины обратной связи. При увеличении глубины положительной обратной связи в пределах от 0 до 1 крутизна амплитудной характеристики увеличивается (см рис. 5б), и при  $BK_0 = 1$  характеристика становится такой же, как у идеального дискриминатора (см. рис. 2д). Однако при  $BK_0 = 1$  усилитель работает неустойчиво.

Рис. 5. Амплитудные характеристики усилителей с положительной обратной связью

усилитель с положительной обратной связью используется обычно при  $BK_0 > 1$ .

Разность  $U_{\text{п2}} - U_{\text{п1}}$  называется *гистерезисом* схемы, величина которого определяет минимальное (предельное) значение амплитуды импульса, запускающего схему.

Одной из основных характеристик дискриминатора является также *чувствительность* – минимальное значение порогового напряжения, при котором обеспечиваются требования к его стабильности. Чувствительность складывается из величины гистерезиса и из величины, характеризующей нестабильность нижнего уровня (порога выключения). Чем больше гистерезис, тем ниже чувствительность дискриминатора.

Поскольку при  $BK_0 > 1$   $|\operatorname{tg}\alpha| = K_0/(BK_0 - 1)$ , то величина гистерезиса (см. рис. 5в)

При дальнейшем увеличении глубины положительной обратной связи ( $BK_0 > 1$ ) коэффициент усиления становится отрицательным (пунктирная прямая на рис. 5в). Для  $BK_0 > 1$ , как видно из рис. 5в, дискриминатор переходит в состояние «1» при достижении, так называемого порога срабатывания  $U_{\text{п1}}$  и возвращается в исходное состояние «0» при уменьшении амплитуды входного сигнала до величины  $U_{\text{п2}} < U_{\text{п1}}$ , называемой порогом выключения. В качестве активного дискриминатора

$$U_{\Gamma} = \frac{U_2 - U_1}{K_0} (BK_0 - 1),$$

где  $U_1$ ,  $U_2$  –минимальное и максимальное значения выходного напряжения усилителя. Следовательно, величина гистерезиса пропорциональна глубине обратной связи. С гистерезисом тесно связано быстродействие дискриминатора: чем больше глубина положительной обратной связи, тем выше быстродействие, но при этом увеличивается гистерезис. Полностью устранить гистерезис невозможно.

Активные дискриминаторы, построенные по рассмотренному выше принципу, в которых используется положительная гальваническая обратная связь, называют триггерами Шмитта. Отличительной особенностью триггера Шмитта является то, что он переключается (переходит из состояния «0» в состояние «1») только на время, когда входное напряжение превышает некоторые пороговые значения. Благодаря положительной обратной связи переход схемы из одного состояния в другое происходит скачкообразно. Триггер Шмитта обладает гистерезисом. При этом его выходное напряжение имеет постоянную величину, не зависящую от входного сигнала. Поэтому триггер Шмитта стандартизирует сигнал только по амплитуде, а длительность выходного сигнала зависит от формы и длительности входного сигнала, а также порога дискриминации. Поэтому длительность выходного сигнала триггера Шмитта меняется в зависимости от амплитуды и длительности входного сигнала.

У другого типа активных дискриминаторов, так называемых формирователей, длительность выходного сигнала определяется самой схемой и также как и амплитуда не зависит от входного сигнала. Разновидностью формирователей являются устройства с положительной емкостной обратной связью – так называемые, *одновибраторы*. Коэффициент обратной связи в случае емкостной положительной связи является динамической величиной, задается значением емкости и частотными характеристиками усилителя и цепи обратной связи. Так же как и в случае триггера Шмитта коэффициент обратной связи определяет гистерезис и, следовательно, чувствительность одновибратора. Иногда для построения активных дискриминаторов используют комбинацию компаратора и выходного формирователя.

Активные дискриминаторы, как типа триггера Шмитта, так и формирователи могут быть реализованы различными способами – на транзисторах, туннельных диодах, операционных усилителях, логических элементах. В частности, высокочувствительные

интегральные дискриминаторы типа триггера Шмитта или одновибратора в последнее время реализуются в основном на компараторах в интегральном исполнении (см. рис. 5). Ниже будет подробнее рассмотрена схема реализации формирователя типа одновибратор на логических элементах типа «2И-НЕ».

### 3. ИНТЕГРАЛЬНЫЕ ЛОГИЧЕСКИЕ СХЕМЫ

Упомянутый в первой части активный амплитудный дискриминатор является примером решения с помощью электронной схемы некоторой логической задачи, а именно установлением факта наличия или отсутствия сигнала, превышающего заданный пороговый уровень напряжения. В случае амплитудного дискриминатора типа формирователя параметры сигнала не имеют значения, так как выходной сигнал формируется самим дискриминатором. В общем случае решения логической задачи электронными средствами выходной сигнал является функцией ряда одновременно приложенных входных сигналов. Так, в схемах совпадений, только при наличии сигналов на всех входах на выходе возникает сигнал.

Логические задачи приходится решать в различных областях науки и техники, в особенности, в вычислительной технике, автоматических системах управления и др. Зависимость между выходным сигналом и рядом одновременно приложенных входных сигналов может быть весьма сложной (особенно при большом числе входных сигналов).

Математически эта зависимость описывается так называемой переключательной функцией. Входные и выходные сигналы могут принимать только два значения («0» или «1»), поэтому переключательная функция оперирует двоичными переменными. Анализ и преобразование переключательной функции подчинены законам алгебры логики.

В основе алгебры логики лежат следующие основные операции.

Логическое сложение (дизъюнкция) переменных  $x_1$  и  $x_2$  – операция, при которой результат сложения у будет равен 1, если хотя бы одна из переменных равняется 1. Обозначается логическое сложение знаком «+» или  $V$ . Схемы, реализующие операцию логического сложения, называются схемами ИЛИ, или схемами сборки.

Функция логического сложения двух переменных  $y=x_1+x_2$  может быть представлена в виде таблицы 1.

Таблица. 1

| $x_1$ | $x_2$ | $y$ |

|-------|-------|-----|

| 1     | 1     | 1   |

| 1     | 0     | 1   |

| 0     | 1     | 1   |

| 0     | 0     | 0   |

Для  $m$  переменных функция ИЛИ записывается:

$$y = x_1 + x_2 + \dots + x_m = \sum_{i=1}^m x_i.$$

Такие таблицы называются таблицами истинности.

Логическое умножение (конъюнкция) переменных  $x_1$  и  $x_2$  – операция, при которой результат будет равен 1 тогда и только тогда, когда обе переменных равны 1. Обозначается логическое умножение так же, как обычное умножение точкой или знаком & или  $\Lambda$ . Схемы, реализующие операцию логического умножения, называются схемами И, или схемами совпадения. Функция логического умножения двух переменных  $y=x_1 \cdot x_2$  описывается таблицей 2.

Таблица 2

| $x_1$ | $x_2$ | $y$ |

|-------|-------|-----|

| 1     | 1     | 1   |

| 1     | 0     | 0   |

| 0     | 1     | 0   |

| 0     | 0     | 0   |

Функция И для  $m$  переменных записывается:

$$y = x_1 \cdot x_2 \cdot x_3 \dots x_m = \prod_{i=1}^m x_i.$$

Логическое отрицание (инверсия) – операция, в результате которой значение входной переменной  $x$  инвертируется (меняется на противоположное). Функция логического отрицания записывание  $y=\bar{x}$ . Схемы, реализующие операцию логического отрицания, называются схемами НЕ, или инверторами.

Операции логического сложения, умножения и инверсии являются основными, так как реализующие их схемы позволяют построить сколь угодно сложное двоичное переключающее устройство.

Две функции  $y_1$  и  $y_2$  называются равносильными (эквивалентными), если они принимают равные значения для каждой комбинации значений переменных. Равносильность обозначается  $y_1=y_2$ .

Наиболее простая структура переключающего устройства, реализующего данную переключательную функцию  $y$ , может быть получена с использованием основных законов алгебры логики. Эти законы записываются для операций логического сложения и умножения следующим образом:

1) переместительный закон

$$x_1 + x_2 = x_2 + x_1$$

$$x_1 \cdot x_2 = x_2 \cdot x_1$$

2) сочетательный закон

$$(x_1+x_2)+x_3=x_1+(x_2+x_3)$$

$$(x_1 \cdot x_2) \cdot x_3=x_1 \cdot (x_2 \cdot x_3)$$

3) распределительный закон

$$x_1 \cdot x_2 + x_1 \cdot x_3 = x_1 \cdot (x_2 + x_3)$$

$$x_1 + x_2 \cdot x_3 = (x_1 + x_2) \cdot (x_1 + x_3)$$

4) закон инверсии

$$\overline{x_1} + \overline{x_2} = \overline{x_1 \cdot x_2}$$

$$\overline{x_1 \cdot x_2} = \overline{x_1} + \overline{x_2}$$

### Логические элементы.

Логическим элементом (схемой) называется дискретно действующее устройство, физически реализующее заданную в аналитической форме или в форме таблицы логическую связь входных и выходных переменных. В общем случае такое устройство имеет  $m$  входов и один выход. На функциональных (структурных) схемах оно изображается в виде прямоугольника, внутри которого обозначается вид выполняемой логической операции.

Для представления логических переменных в электронных логических схемах используются электрические сигналы. Различают потенциальный и импульсный способы представления логических переменных. Возможно также импульсно-потенциальное представление.

Цифра 0 обычно представляется низким потенциалом ( $E_0$ ) или отсутствием импульса, 1 – высоким потенциалом ( $E_1$ ) или наличием импульса.

Так как в электронных схемах на полупроводниковых элементах используется как положительное, так и отрицательное питающее напряжение (например, для p-n-p транзисторов – отрицательное, для n-p-n – положительное), то иногда пользуются понятием отрицательная и положительная логика. Для положительной логики 0 представляется низким уровнем, 1 – высоким. Для отрицательной – наоборот.

Для построения двоичных переключательных устройств широко используются электронные ключи. Ключи могут быть построены на электровакуумных, полупроводниковых или каких-либо других нелинейных приборах. Они должны иметь малое и весьма стабильное внутреннее сопротивление во включенном состоянии и возможно большее в выключенном, высокое быстродействие, т.е. высокую скорость перехода ключа из одного состояния в другое, высокую стабильность пороговых уровней.

Пороговые уровни могут изменяться с изменением температуры, из-за нестабильности источников питания и т.п.

В настоящее время наиболее широкое распространение получили полупроводниковые логические схемы. Они могут быть выполнены на различных элементах: диодах, транзисторах или их комбинации.

Уровни входных и выходных потенциалов зависят от вида используемых в логической схеме нелинейных приборов и от величины питающего напряжения. Например, для схем с транзисторами типа р-п-р эти потенциалы отрицательны, а для схем с транзисторами п-р-п – положительны, величина же их обычно лежит в пределах  $(0 \div 10)$  В. В диодных схемах входные и выходные потенциалы могут быть положительными и отрицательными.

Логические элементы могут быть выполнены на диодах и транзисторах. Построение переключательных цепей с использованием только диодных ключей не всегда возможно. Это обусловлено тем, что посредством диодных ключей невозможно реализовать операцию инверсии, кроме того, диодный ключ вызывает определённое ослабление сигнала, что ограничивает допустимое число последовательно включённых схем. Эти недостатки диодных ключей можно устранить, используя для построения переключательных цепей наряду с диодными ключами транзисторные ключи.

#### Классификация универсальных логических элементов

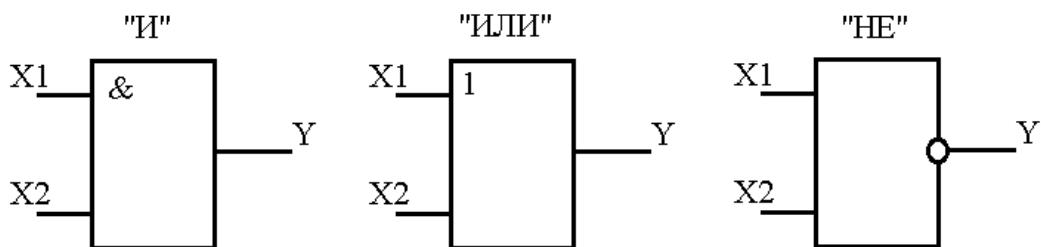

Операции логического умножения и логического сложения реализуются простейшими переключательными схемами – многовходовыми диодно-резистивными ключами, а третья логическая операция – инверсия (НЕ) – реализуется посредством транзисторных ключей. Таким образом, используя электронные ключи, можно построить любое сколь угодно сложное переключающее устройство.

Рис. 6. Условные обозначения универсальных логических элементов.

Схемы И (ИЛИ) обладают свойством обратимости. Это свойство состоит в том, что схема И для положительных сигналов

(высокого уровня) является схемой ИЛИ для сигналов низкого уровня и наоборот. Это свойство обратимости схем И (ИЛИ) является общим и не зависит от того, на каких элементах данная схема реализована. Учитывая свойство обратимости логических схем И и ИЛИ, для построения переключательных схем достаточно использовать только два логических элемента из трёх основных, а именно: элементы И и НЕ или элементы ИЛИ и НЕ. Обычно эти пары элементов объединены в единый универсальный логический элемент, при помощи которого можно построить любую переключательную цепь. Условное обозначение универсальных элементов в функциональных схемах показано на рис. 6.

В зависимости от способа построения схем И и ИЛИ различают следующие виды универсальных логических элементов: транзисторные с непосредственными связями, диодно-транзисторные и транзисторно-транзисторные. Эти элементы используются для построения более сложных переключательных схем, образующих системы транзисторной логики с непосредственными связями (ТЛНС), диодно-транзисторной логики (ДТЛ) и транзисторно-транзисторной логики (ТГЛ).

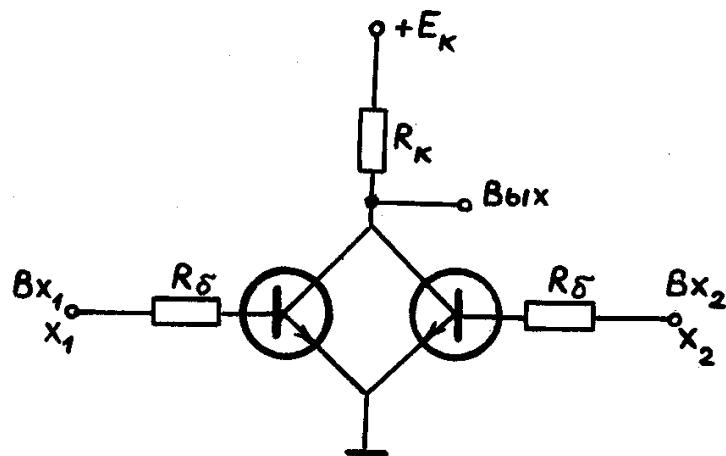

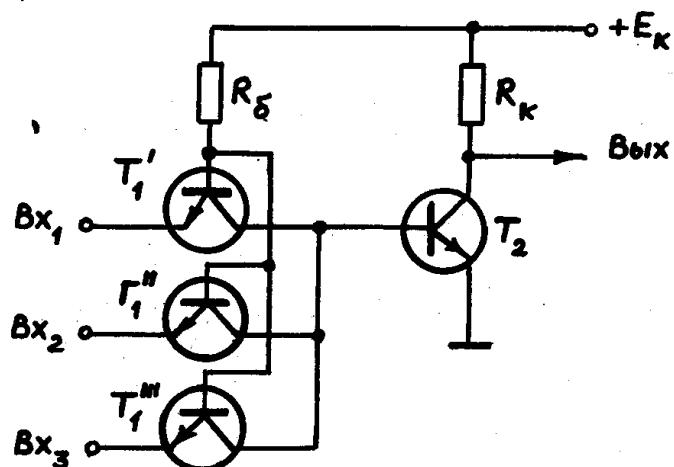

Рис. 7. Транзисторный элемент с непосредственными связями.

На рис. 7 дана схема двухходового универсального транзисторного элемента с непосредственными связями, являющаяся схемой ИЛИ-НЕ для сигналов высокого уровня ( $E_1 \approx +E_k$ ,  $E_o \approx 0$ ) и схемой И-НЕ для сигналов низкого уровня ( $E_1 \approx 0$ ,  $E_o = E_k$ ). Если на  $V_{x_1}$  и  $V_{x_2}$  элемента поданы низкие уровни ( $V_{\text{вх}} \approx 0$ ), то оба транзистора заперты, и на выходе – высокий уровень ( $V_{\text{вых}} \approx E_k$ ). При подаче хотя бы на один вход высокого уровня, обеспечивающего насыщение транзистора, напряжение на выходе будет иметь низкий уровень  $V_{\text{вых}} = V_{\text{кн}} \approx 0$ . Параметры схемы выбираются так, чтобы выполнялось условие надёжного запирания

последующего транзистора при открытом (насыщенному) предыдущем и насыщение последующего при запертом предыдущем.

Основное преимущество элементов ТЛНС – их простота. К недостаткам следует отнести: зависимость устойчивости работы от разброса характеристик транзисторов и их температурных изменений, сравнительно небольшое быстродействие, обусловленное работой транзисторов в режиме глубокого насыщения.

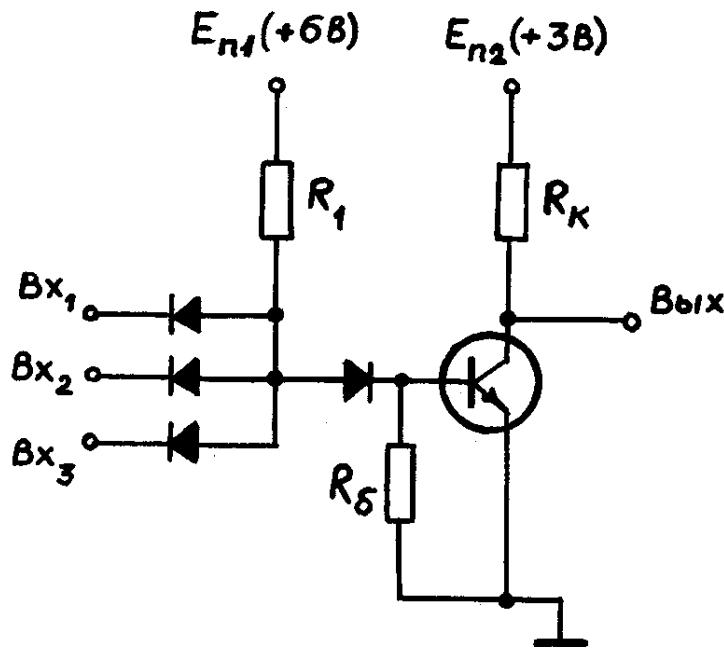

Рис. 8. Базовый элемент ДТЛ.

На рис. 8 приведена схема универсального диодно-транзисторного элемента, образованного соединением многовходового диодного ключа, реализующего операцию И для сигналов высокого уровня с транзисторным ключом, выполняющим функцию инвертора НЕ. Такой элемент реализует операцию И-НЕ.

Параметры схемы выбраны так, чтобы обеспечивалось надёжное запирание и открывание (насыщение) транзистора в зависимости от значений входных сигналов. Если на все три входа диодного ключа подаются сигналы высокого уровня  $E_1 \approx +E_k$ , то в базу транзистора течёт ток, обеспечивающий насыщение транзистора, и на выходе возникает сигнал низкого уровня. Как только хотя бы на один из входов диодного ключа будет подан сигнал низкого уровня  $E_0 \approx 0$ , ток через сопротивление  $R_1$  потечёт во входную цепь, транзистор запрётся, и на выходе появится сигнал высокого уровня. Наибольшее распространение получили диодно-

транзисторные элементы с двумя, тремя, четырьмя и восьмью входами.

По сравнению с элементами ТЛНС диодно-транзисторные элементы обладают большим быстродействием, большей помехозащищённостью и более широкими возможностями объединения по входу и разветвления по выходу.

а)

б)

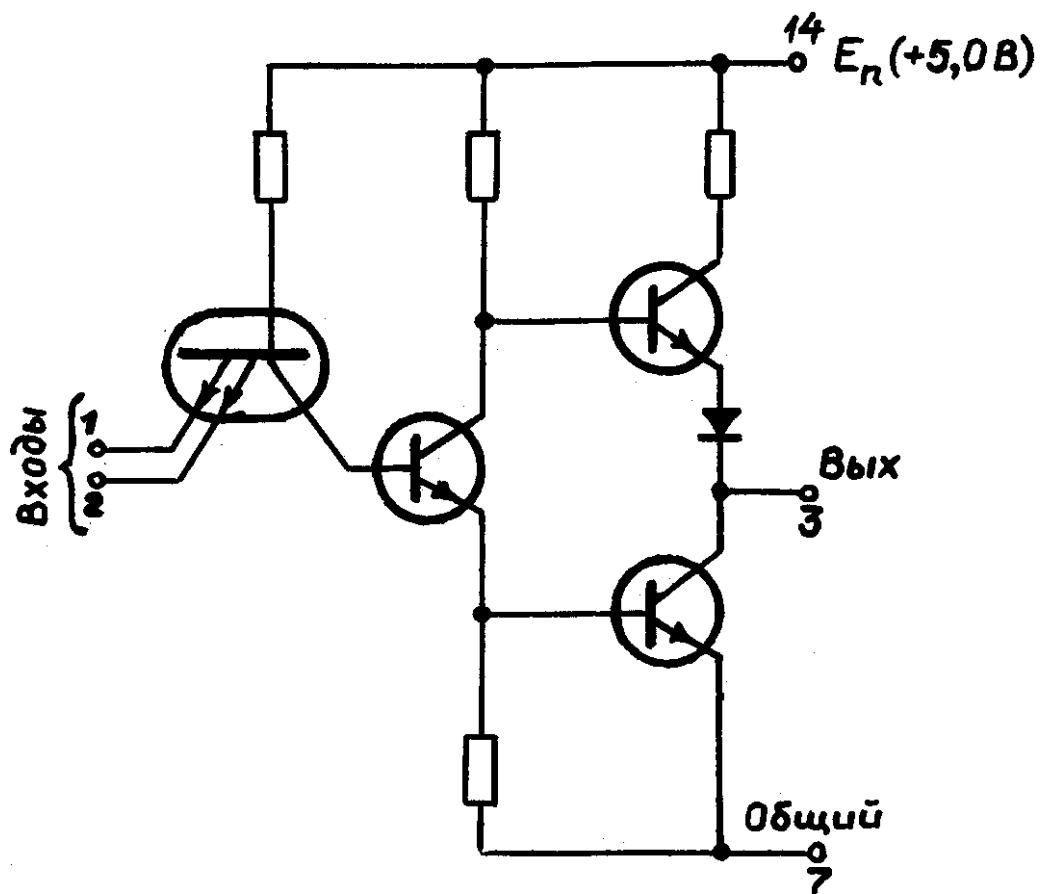

Рис. 9. Транзисторно-транзисторный элемент И-НЕ.

В настоящее время наиболее широко применяются транзисторно-транзисторные логические схемы. Их достоинствами по сравнению с диодно-транзисторными схемами являются большее быстродействие и использование одного источника питания. На рис. 9а изображена схема с тремя входными транзисторами. Входные сигналы управляют током через общий базовый резистор  $R_B$ . Если на один из входов подаётся сигнал низкого уровня  $E_o \approx 0$ , то ток протекает через соответствующий транзистор  $T_1$  во входную цепь,

транзистор  $T_2$  запирается, и на выходе схемы появляется сигнал высокого уровня. Если на все входы подаются сигналы высокого уровня, то ток течёт в базу транзистора  $T_2$  и насыщает его. На выходе схемы появится сигнал низкого уровня.

Обычно в элементах ТТЛ вместо  $m$  входных транзисторов используется один многоэмиттерный транзистор  $T_1$  (рис. 9б). Работа схемы почти не отличается от работы предыдущей схемы, однако она будет рассмотрена более подробно, так как изучается в данной задаче. Схема работает следующим образом. При подаче хотя бы на один из входов сигнала низкого уровня  $E_o \approx 0$  один из эмиттеров транзистора  $T_1$  оказывается под низким потенциалом  $E_o \approx 0$ , его база через резистор  $R_\delta$  соединена с источником напряжения  $+E_k$ , поэтому эмиттерный переход транзистора  $T_1$  открывается. Непосредственно после открытия транзистора  $T_1$  его коллекторный ток быстро разрядит входную ёмкость насыщенного транзистора  $T_2$ , т.е. отберёт из его базы весь избыточный заряд. Это обеспечивает большое быстродействие схемы. Транзистор  $T_2$  запрётся, и на выходе появится сигнал высокого уровня. После запирания транзистора  $T_2$  транзистор  $T_1$  перейдёт в насыщение, так как его нагрузкой будет очень большое сопротивление запёртого транзистора  $T_2$ . Поэтому весь ток, текущий через сопротивление  $R_\delta$ , будет протекать через открытый эмиттерный переход транзистора  $T_1$ . Он является входным током схемы. При подаче на все входы сигналов высокого уровня  $E_1 \approx E_k$  эмиттерные переходы транзистора  $T_1$  запираются. Потенциал базы транзистора  $T_1$  не может следовать за потенциалом эмиттеров, так как он фиксируется открывшимися переходами база-коллектор  $T_1$  и база-эмиттер транзистора  $T_2$ . Теперь весь ток, протекающий через сопротивление  $R_\delta$ , течёт в базу транзистора  $T_2$  и быстро насыщает его. На выходе появляется сигнал низкого уровня  $E_o = V_{кэн} \approx 0$ . Входной ток схемы в этом режиме имеет другое направление и малую величину, так как он является коллекторным током инверсно включённого транзистора  $T_1$ . Коэффициент усиления  $\beta_J$  транзистора  $T_1$  при инверсном включении мал, что обеспечивается структурой транзистора  $T_1$ .

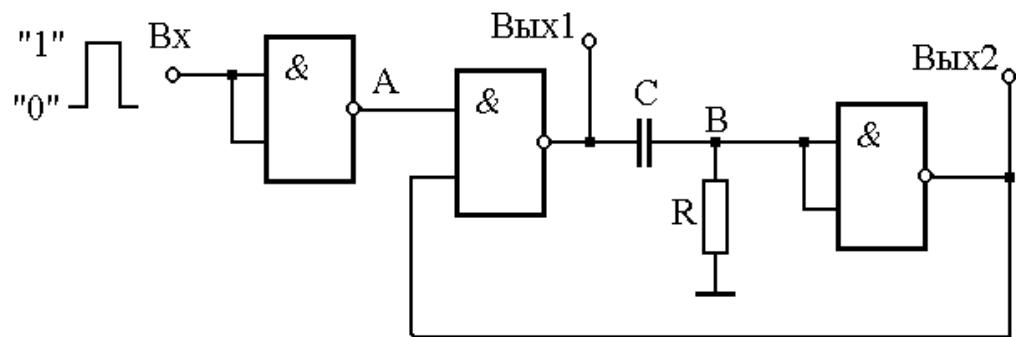

Практические схемы элементов ТТЛ несколько модифицированы по сравнению со схемой рис. 9б. На рис. 11 и рис. 12 даны схемы элементов 155 серии, изучаемые в задаче. В этих схемах применён двухтактный выходной каскад, обеспечивающий малое выходное сопротивление схемы при обоих уровнях входного сигнала. Это повышает быстродействие и нагрузочную способность схемы.

### Системы логических элементов.

Рассмотренные в предыдущем разделе логические элементы называются основными или базовыми. Элементы, имеющие одинаковую структуру (ТЛНС, ДТЛ, ТТЛ и др.) и способ реализации (конструкция и технология изготовления), образуют серию логических элементов. Кроме базовых и других логических элементов в серию могут входить входные и выходные (мощные) усилители и некоторые другие устройства.

По способу реализации различают: системы элементов на дискретных компонентах, системы микромодульных и интегральных элементов.

В настоящее время наиболее перспективной является система интегральных элементов. В зависимости от способа реализации система интегральных элементов включает два класса интегральных схем: монолитные и гибридные.

Монолитные (твёрдые) интегральные схемы образуются путём создания в исходном монолитном полупроводниковом материале (как правило, кремний, реже германий) зон с различными электрическими свойствами (транзистора, диоды, резисторы), соединённых между собой нанесением проводящего слоя определённой конфигурации.

Гибридные интегральные схемы образуются соединением отдельных компонентов, располагаемых на изолирующей подложке. Активные и нелинейные компоненты (транзисторы, диоды) изготавливаются методом твёрдых схем, а пассивные элементы (сопротивления, конденсаторы) – нанесением тонких слоёв материалов с определёнными электрическими свойствами. Отдельные компоненты соединяются проводниками или металлизацией.

Из всех систем логических и линейных элементов наиболее перспективными являются твёрдые интегральные схемы (особенно при крупносерийном производстве). Они превосходят все другие схемы по числу элементов на единицу площади и по надёжности.

Наибольшее распространение получили интегральные твёрдые схемы четырёх типов: транзисторные логические схемы с непосредственными связями (ТЛНС), диодно-транзисторные логические схемы (ДТЛ), транзисторно-транзисторные логические схемы (ТТЛ) и транзисторные логические схемы на переключателях тока (ТЛПТ). ТЛПТ применяются только в интегральном исполнении.

Область и условия применения интегральных твёрдых схем определяются рядом параметров. Это – быстродействие, помехоустойчивость, коэффициенты объединения по входу и

разветвления по выходу, количество номинальных величин питающих напряжений, а также эксплуатационные характеристики (надёжность, потребляемая мощность, объём, устойчивость к механическим и климатическим воздействиям и стоимость).

*Быстродействие* определяется временем задержки и временем нарастания (спада) выходного сигнала. Часто для характеристики быстродействия интегральных твёрдых схем пользуются понятием среднего времени задержки

$$t_{3cp} = \left( t_3^{10} + t_3^{01} \right) / 2,$$

где  $t_3^{10}$  и  $t_3^{01}$  - времена задержки выходного сигнала при переходе схемы из состояния 1 в состояние 0, и из состояния 0 в состояние 1, соответственно.  $t_\phi^{10}$  и  $t_\phi^{01}$  - длительности фронтов выходного сигнала при переходе схемы из состояния 1 в состояние 0 и из состояния 0 в состояние 1. В зависимости от быстродействия интегральные твёрдые схемы делятся на низкоскоростные ( $t_{3cp} \geq 50$  нс), среднескоростные ( $50 \geq t_{3cp} \geq 15$  нс), высокоскоростные ( $15 \geq t_{3cp} \geq 5$  нс) и сверхскоростные ( $t_{3cp} \leq 5$  нс).

*Коэффициент объединения по входу (M)* характеризует возможности логических элементов по объединению входных сигналов. Величина M ограничивается сложностью схемы и её помехоустойчивостью и обычно  $2 \leq M \leq 8$ .

*Коэффициент разветвления по выходу (N)* характеризует нагрузочную способность схемы, т.е. определяет, каким числом аналогичных схем может быть нагружена данная схема. Для большинства интегральных твёрдых схем значения N находятся в пределах от 3 до 15.

Помехоустойчивость оценивается наибольшим допустимым напряжением, наводимым на входе схемы вследствие ёмкостных и индуктивных связей, а также по цепям питания и земле, гарантирующим нормальную работу схемы.

#### **4. ФОРМИРОВАТЕЛЬ НА ЛОГИЧЕНСКИХ ЭЛЕМЕНТАХ ТИПА 2И-НЕ**

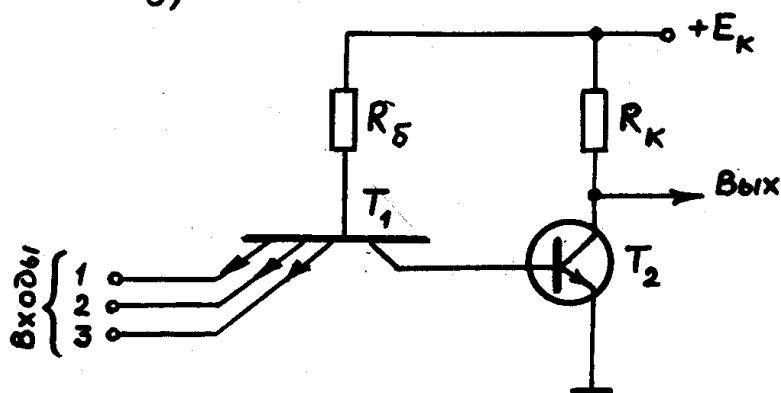

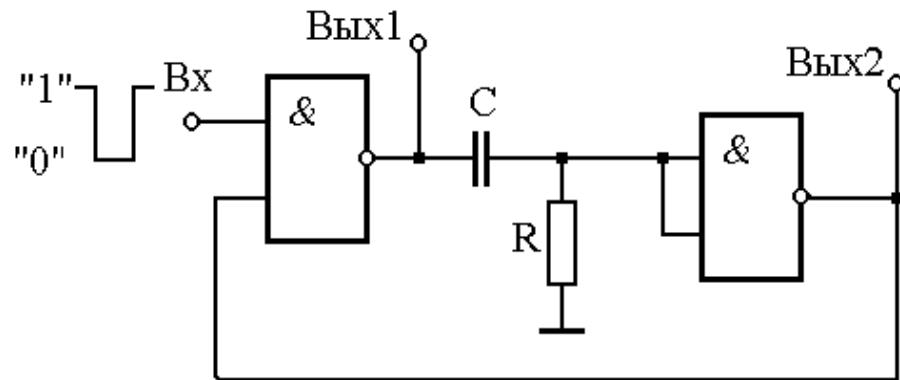

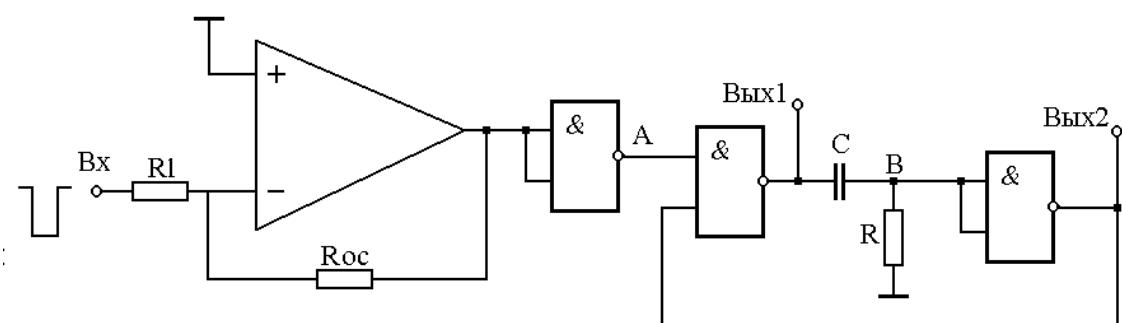

Принципиальная схема формирователя – одновибратора на логических элементах 2И-НЕ типа ТТЛ изображена на рис. 10. Логической «1» для этих элементов соответствует напряжение питания (+5 В), логическому «0» – нулевое напряжение («земля»). В исходном состоянии на входе схемы должен присутствовать уровень напряжения, соответствующий логической «1». Поскольку точка А

схемы соединена с землей через относительно небольшое сопротивление  $R \approx 1.2$  кОм, напряжение в этой точке в исходном состоянии соответствует уровню «0». Поэтому на выходе второго логического элемента 2И-НЕ будет напряжение, соответствующее уровню «1». Поскольку выход второго логического элемента соединен с одним из входов первого, в исходном состоянии уровень «1» присутствует на обоих входах первого логического элемента. Это означает, что на его выходе будет нулевой уровень напряжения.

Рис. 10. Одновибратор на логических элементах.

Для того, чтобы схема сработала, на ее вход следует подать такой сигнал, чтобы уровень входного напряжения изменился – вместо логической «1» стал логический «0» (другими словами необходимо подать отрицательный перепад напряжения). Тогда на выходе первого логического элемента появится напряжение, соответствующее «1». Поскольку, конденсатор в исходном состоянии не был заряжен, разность потенциалов между его обкладками была равна нулю. В момент скачка эта разность должна сохраняться, поэтому логическая «1» поступит на вход второго логического элемента и переключит его в состояние «0» на выходе. В свою очередь, нулевое напряжение окажется и на втором входе первого логического элемента. По мере заряда конденсатора, напряжение в точке А будет уменьшаться, однако пока оно не достигнет уровня переключения «0/1» на выходе второго логического элемента будет сохраняться нулевое напряжение. Благодаря этому на выходе первого элемента напряжение будет держаться на уровне, соответствующем логической «1» даже и после окончания действия входного сигнала. Как только конденсатор зарядится настолько, что напряжение в точке А упадет до уровня, при котором на выходе второго логического элемента появится логическая «1», схема вернется в исходное состояние. При этом на ее выходах 1 и 2 будут сформированы инвертированные друг

относительно друга импульсы, длительность которых будет определяться величиной  $RC$ . Разумеется, если длительность входного сигнала будет превышать собственное время формирования, то и длительность выходного импульса будет определяться длительностью входного сигнала. Таким образом, данная схема работает в качестве формирователя только на удлинение сигналов.

Для того, чтобы схема срабатывала от сигналов положительной амплитуды, их надо подавать на формирователь через инвертор (см. рис. 11).

Рассмотренная схема имеет фиксированный порог дискриминации  $U_n^0$ , определяемый уровнем перехода логического элемента из состояния «1» в состояние «0» (в случае схемы на рис. 11) или уровнем перехода логического элемента из состояния «0» в состояние «1» (в случае схемы на рис. 10). Чтобы на основе такого одновибратора построить амплитудный дискриминатор с регулируемым порогом, очевидно, необходимо подавать сигналы на его вход через усилитель с регулируемым коэффициентом усиления  $K$ . В этом случае порог дискриминации всей схемы  $U_n = U_n^0/K$ . Более типичным является использование компаратора на входе одновибратора вместо усилителя. При этом регулирование порога дискриминации осуществляется подбором напряжения смещения на втором входе компаратора (обычно с помощью резистивных делителей напряжения).

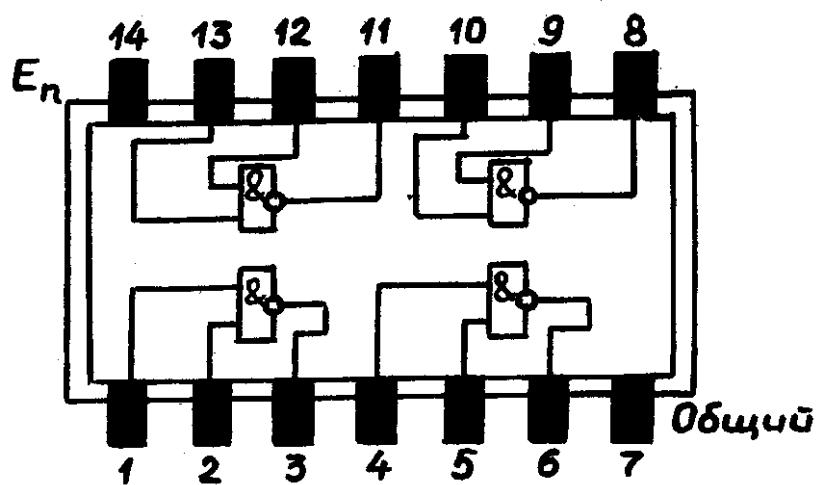

## 5. ЗАДАНИЕ

1. Построить одновибратор на логических элементах типа 2И-НЕ, используя микросхемы К155ЛА3. Схема одновибратора изображена на рис. 11. На рис. 13 представлены схема, иллюстрирующая устройство микросхемы К155ЛА3 и принципиальная схема одного логического элемента. Электрические параметры микросхемы указаны в Таблице 3. Емкость конденсатора  $C$  следует рассчитать на основе заданного преподавателем значения величины  $RC$ , при этом сопротивление  $R$  следует выбрать равным 1.2 кОм.

2. Подать на вход одновибратора сигнал в виде прямоугольного импульса положительной полярности от генератора. Амплитуду импульса установить равной 2 В, длительность  $\sim 0.5RC$ . Убедиться, что схема работает в режиме одновибратора. С помощью осциллографа построить эпюры напряжения (временные диаграммы) на входе схемы, на выходах 1 и 2, а также в точках А, В.

3. Измерить амплитудную характеристику – зависимость амплитуды сигнала на выходе 1 от амплитуды входного импульса –  $U_{\text{вых}}(U_{\text{вх}})$ . Для этого увеличивать амплитуду  $U_{\text{вх}}$  в диапазоне от 0 В до ~5 В, а затем уменьшать амплитуду  $U_{\text{вх}}$  в обратном порядке. По амплитудной характеристике определить порог срабатывания схемы  $U_{\text{п}}^0$  и измерить ее гистерезис.

4. Измерить зависимость длительности выходного сигнала от длительность входного импульса в диапазоне длительностей входного импульса от ~0.1RC до ~10RC. Измерить длительность выходного импульса в зависимости от разных значений величины RC. При этом сопротивление R менять не следует, а емкость конденсатора следует выбирать как больше, так и меньше исходной. Убедиться, что длительность выходного сигнала определяется величиной RC, при этом проверить, равна ли она в точности RC.

5. Построить на базе одновибратора дискриминатор амплитуды. Для этого подключить к входу одновибратора инвертирующий усилитель на основе операционного усилителя 544УД2 (см. рис. 12). Рассчитать параметры схемы инвертирующего усилителя по заданной преподавателем величине коэффициента усиления с обратной связью  $K_{\text{ОС}}$ . Подать на вход усилителя сигнал от генератора отрицательной полярности амплитудой 0.2-0.5 В, длительностью ~0.5RC. Убедиться, что на выходе одновибратора появляется сформированный сигнал. Меняя амплитуду сигнала на входе усилителя измерить порог срабатывания всей схемы  $U_{\text{п}}$ . Убедиться, что  $U_{\text{п}} = U_{\text{п}}^0 / K_{\text{ОС}}$ .

## ЛИТЕРАТУРА

1. Н.Н.Дмитриева, А.С.Ковтюх, Б.Х.Кривицкий. Ядерная электроника. М.: Изд. МГУ. 1982. Гл. 5.

2. П.Хоровиц, У.Хилл. Искусство схемотехники. М.: Мир. 1983. т.1.

3. А.П.Щитович. Ядерная электроника. М.: Энергоатомиздат. 1984.

4. В.А.Григорьев, А.А.Колюбин, В.А.Логинов. Электронные методы ядерно-физического эксперимента. М.: Энергоатомиздат. 1988.

5. Х.Шмидт. Измерительная электроника в ядерной физике. М.: Мир. 1989.

Рис. 11. Принципиальная схема одновибратора на логических элементах типа 2И-НЕ с входным инвертором.

Рис. 12. Принципиальная схема дискриминатора амплитуды на основе инвертирующего усилителя и одновибратора на логических элементах.

Рис. 13. а: четыре двухвходовых логических элемента И-НЕ микросхемы К155ЛА3; б: принципиальная схема одного двухвходового элемента И-НЕ.

Таблица 3.

ЭЛЕКТРИЧЕСКИЕ ПАРАМЕТРЫ К155ЛА3

|                                                                      |          |

|----------------------------------------------------------------------|----------|

| Напряжение источника питания .....                                   | +5 В ±5% |

| Потребляемая мощность (на один логический элемент)<br>не более ..... | 25 мВт   |

| Напряжение выходного сигнала 1 не менее .....                        | 2,4 В    |

| Напряжение выходного сигнала 0 не более .....                        | 0,4 В    |

| Время задержки распространения не более .....                        | 18,5 нс  |

| Коэффициент разветвления по выходу не более:                         |          |

| для К1ЛБ553 .....                                                    | 10       |

| для К1ЛБ5511 .....                                                   | 5        |

| Коэффициент объединения по входу И не более .....                    | 2        |

| Напряжение статической помехи не более .....                         | 0,4 В    |